Terasic has officially introduced the Atum Nios V Starter Kit, a feature-rich evaluation platform built around the RISC-V-based Nios V processor. The kit is aimed at embedded engineers, system developers, and educators, helping them accelerate development with Intel Altera’s Nios V processors and Agilex 3 FPGAs. It addresses common pain points in RISC-V adoption such as long design verification cycles and complex hardware integration.

Core Architecture

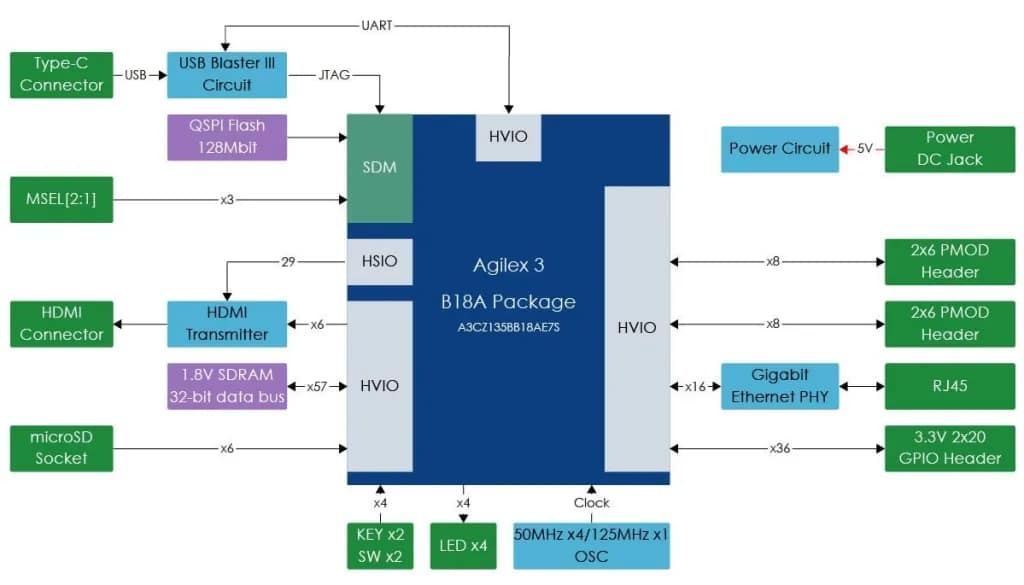

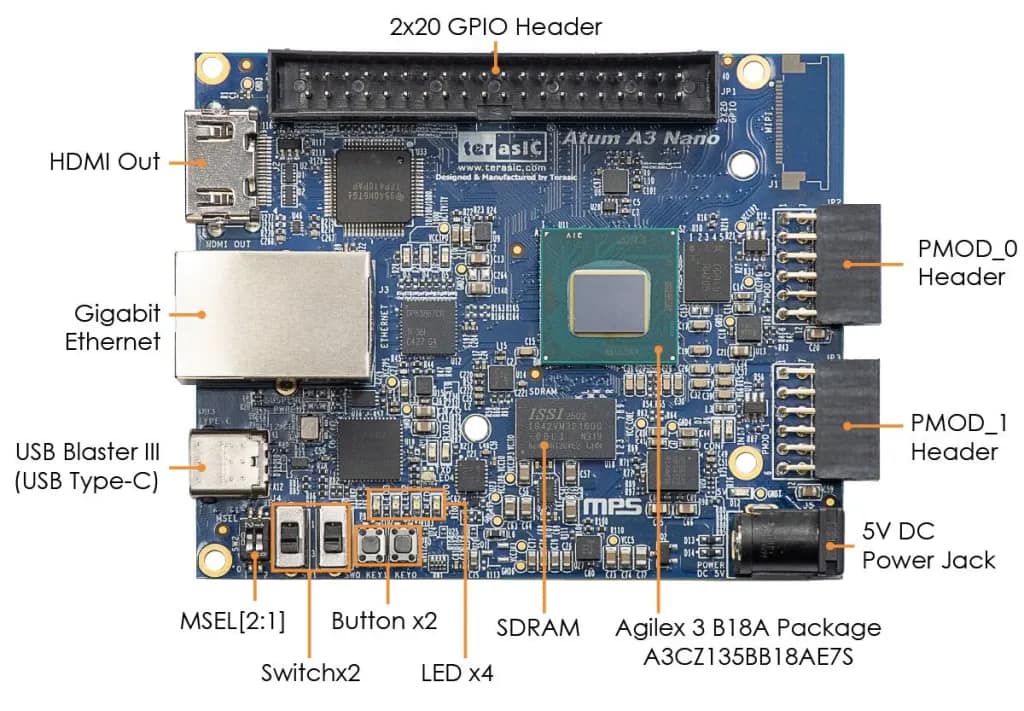

At the heart of the kit is the Atum A3 Nano board, featuring the Agilex 3 A3CZ135BB18AE7S FPGA. This device integrates 135,110 logic elements, on-chip memory blocks, DSP multipliers, and multiple PLLs. Together, these resources provide a flexible balance of performance and adaptability for embedded processing tasks and signal-heavy workloads like image processing or intelligent device control.

Atum Nios V Block Diagram

| Atum Nios V Starter Kit - Quick Specs | |

|---|---|

| FPGA | Agilex 3 A3CZ135BB18AE7S (135,110 LEs) |

| Processor | RISC-V based Nios V |

| Memory | 64MB SDRAM, 128Mbit QSPI Flash, microSD slot |

| Connectivity | Gigabit Ethernet, USB Blaster III (Type-C) |

| Display | HDMI output (up to 1080p @ 60Hz) |

| I/O | 1× 2×20 GPIO, 2× 2×6 TMD GPIO (PMOD), 4 LEDs, 2 switches, 2 buttons |

| Board Size | 85 × 70 mm |

| Price | 179 USD |

Hardware Overview

The Atum Nios V board comes with a configuration designed specifically for RISC-V embedded development:

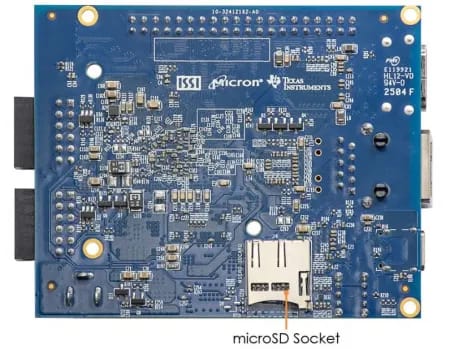

- Memory: 64MB SDRAM with a 32-bit data bus, 128Mbit QSPI Flash for fast boot/configuration, and a microSD card slot for external storage.

- Connectivity: Gigabit Ethernet, UART, and an HDMI output enabled by TI’s TFP410 transmitter. The HDMI interface supports resolutions up to 1080p @ 60Hz (WUXGA), making it suitable for graphics-intensive use cases.

- Expansion: One 2×20-pin GPIO header and two 2×6-pin TMD GPIO connectors (PMOD-compatible) for attaching sensors, actuators, or other peripherals.

- I/O: Four user LEDs, two push buttons, and two slide switches for quick testing and prototyping.

- Debug: On-board USB Blaster III (Type-C interface) for FPGA and processor debugging.

Licensing and Software Support

One key advantage of the kit is its bundled software and IP licensing:

- 1-year license for Intel’s Triple-Speed Ethernet IP core (no additional cost).

- Free access to the Quartus Prime Pro design suite for Agilex 3 FPGAs.

This combination lowers the entry barrier for RISC-V development, enabling engineers to quickly validate hardware/software co-designs across multiple application domains such as robotics, automotive systems, smart infrastructure monitoring, image processing terminals, and consumer IoT devices.

Atum Nios V Top View

Educational and Developer Resources

Beyond hardware, Terasic provides developer-friendly documentation and examples:

- User manual and Quick Start Guide

- Sample projects: My First FPGA and My First Nios V

- Reference designs for SD card file system setup, HDMI display debugging, SDRAM access tests, and UART communication

These materials make the kit accessible to both beginners and experienced developers, significantly reducing the time from concept to working prototype.

Technical Specifications

FPGA

- Device: Agilex 3 A3CZ135BB18AE7S

- Logic elements: 135,110

- Memory: 6.89 Mbit M20K blocks, 1.4 Mbit MLAB blocks

- Multipliers: 368 × 18×19 multipliers

- PLLs: 4 I/O PLLs + 8 architectural PLLs

Memory

- SDRAM: 64MB, 32-bit bus

- Storage: microSD slot, 128Mbit QSPI Flash

Display

- HDMI via TI TFP410 transmitter

- Up to 1080p @ 60Hz (WUXGA support)

Connectivity

- 1× Gigabit Ethernet

- On-board USB Blaster III (USB Type-C)

I/O

- 1× 2×20 GPIO header (3.3V)

- 2× 2×6 TMD GPIO headers (3.3V, PMOD-compatible)

- 4× LEDs, 2× slide switches, 2× push buttons

Power

- 5V DC input via barrel jack

Mechanical

- Dimensions: 85 × 70 mm

Kit Contents & Pricing

The package includes:

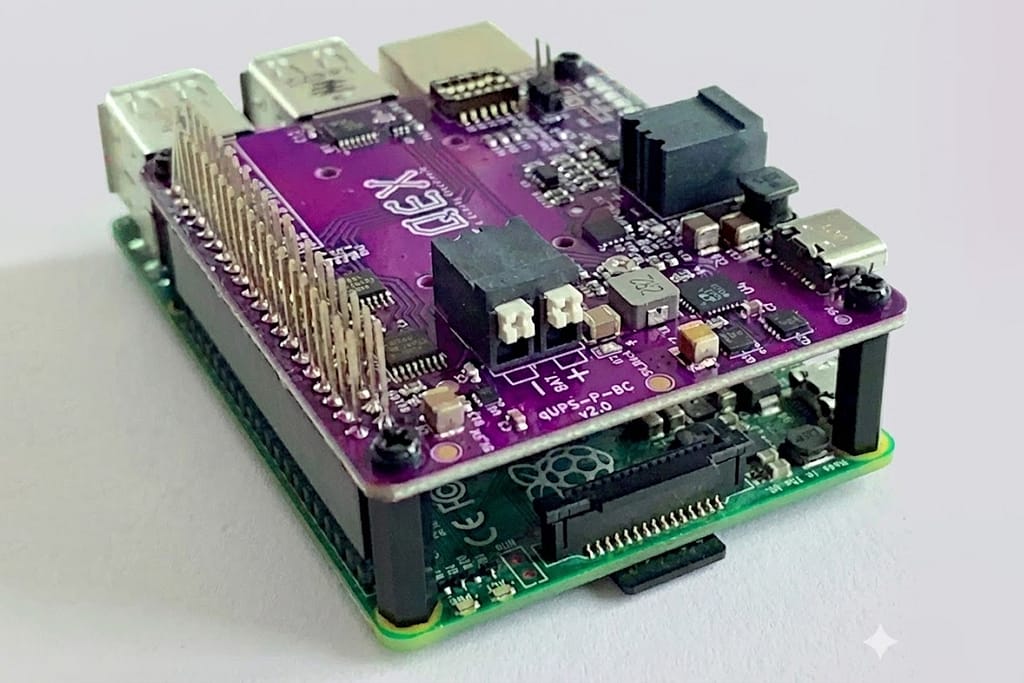

- Atum A3 Nano board (with pre-installed heatsink and acrylic enclosure)

- USB Type-C cable

- 5V/2A DC power adapter

According to Terasic’s official website, the Atum Nios V Starter Kit is priced at $179 USD.

The Atum Nios V Starter Kit combines Agilex 3 FPGA hardware, a RISC-V-based Nios V processor, bundled IP licensing, and rich educational resources into a single package. It delivers a cost-effective, ready-to-use solution for embedded development, academic research, and system prototyping—making it an attractive option for engineers and educators exploring RISC-V in FPGA environments.

For more technical details or ordering information, visit Terasic’s official website.